# European HPC RISC-V Roadmap Workshop @ HiPEAC 2023

John D. Davis, Ph.D.

Director, Laboratory for Open Computer Architecture RISC-V Int'l SIG HPC Chair

## **Overview**

RISC-V Ecosystem

• SIG HPC

RISC-V Research

RISC-V is HPC!

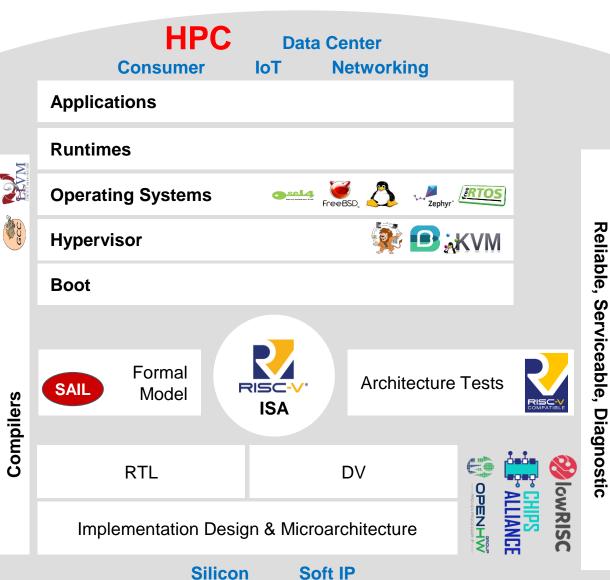

## **RISC-V Ecosystem**

Services

Performance

Security

Debug

Barcelona

Supercomputing

Center

Centro Nacional de Supercomputación

O Buildbot

**Training Research**

Academia

SAIL

SPIKE

**EMU**

Simulators

**Tools**

Analysis

Profilers +

CI/Testing

# **Special Interest Group for HPC**

## SIG-HPC Vision & Mission: RISC-V: IoT to HPC

#### **Vision:**

The technical and strategic imperatives that guide the RISC-V ecosystem development to enable an Open HPC Ecosystem...

#### Mission:

...enable RISC-V in a broader set of new software and hardware opportunities in the High Performance Computing space, from the edge to supercomputers, and the software ecosystem required to run legacy and emerging (AI/ML/DL) HPC workloads.

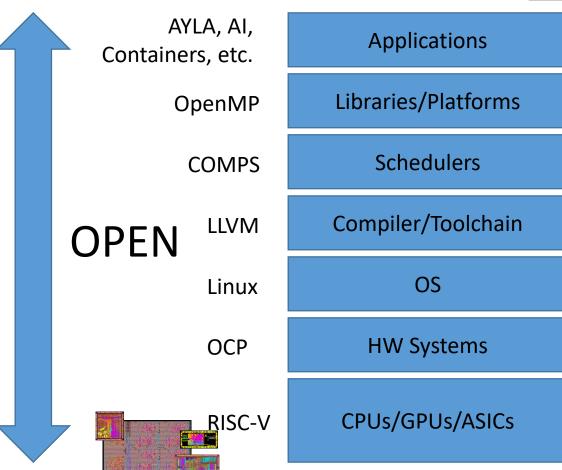

## SIG-HPC: An Open era of HPC!

- CPUs, Accelerators, other hardware units, and coprocessors

- Verification and compliance infrastructure and methodologies specific to HPC

- Alignment and engagement and IP enablement.

- RISC-V software ecosystem alignment

- Engage and represent RISC-V in compute intensive industry and academic events

- Identify key industrial and academic partners.

- Support global technology independence with a RISC-V ecosystem roadmap and partners

#### **SIG-HPC Initiatives**

- Guide and enable the community

- Virtual Memory

- SV57, SV57K, SV64, SV128

- HPC SW & HW ecosystem & roadmap

- Accelerators

- ISA Extensions

- HPC Software Stack

- Starting with HPC Libraries

- RISC-V Testbeds

- Adapters/Devices: Infiniband, GPUs, etc.

## Join the RISC-V Int'l SIG HPC

# **RISC-V HPC Research in Europe**

## **European RISC-V R&D**

- 2019: What is Open Source Hardware??

- 2020: Open Source Hardware

- 2021: RISC-V? Roadmap?

- November roadmap report

- Horizon Europe Work Programme 2021-22:

- Open Source Hardware (OSH) appears 6 times

- CSA Roadmap

- 2022: Build RISC-V!!!

- KDT JU Work Programme 2021 v13:

- RISC-V appears 25 times / OSH appears 2 times

- EU Chip Act (collection of documents)

- RISC-V and OSH appears 5 each

- 2023 has more to come! (EuroHPC, KDT/Chip JU, etc.)

- TRISTAN, ISOLDE, ...

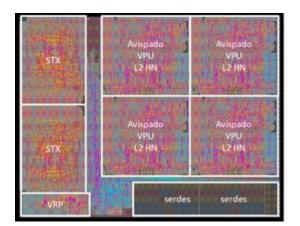

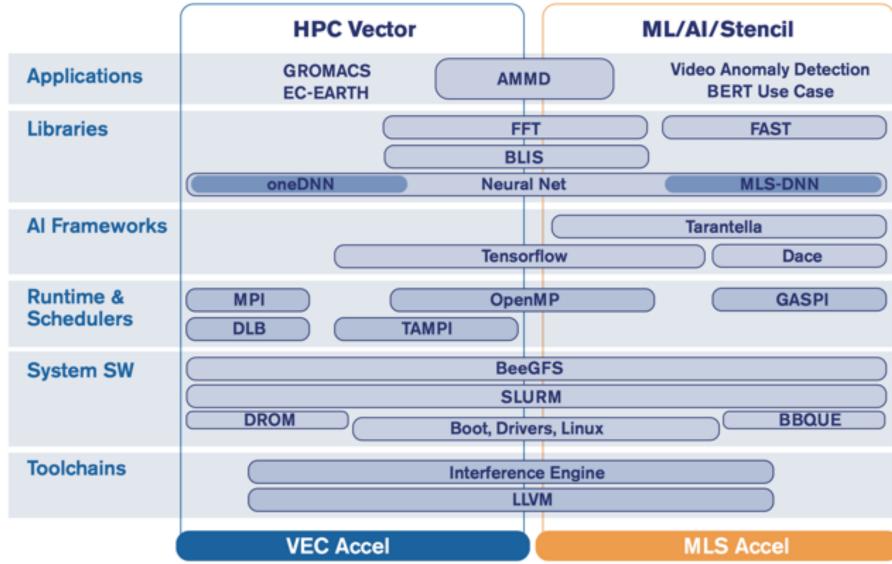

## **RISC-V Hardware Activities**

- EPI

- Vector Processor

- Machine Learning and Stencil accelerator

- Variable Precision CPU (High Precision)

- MEEP

- Vector and systolic arrays coprocessors

- eProcessor

- OOO Single and multicore chips

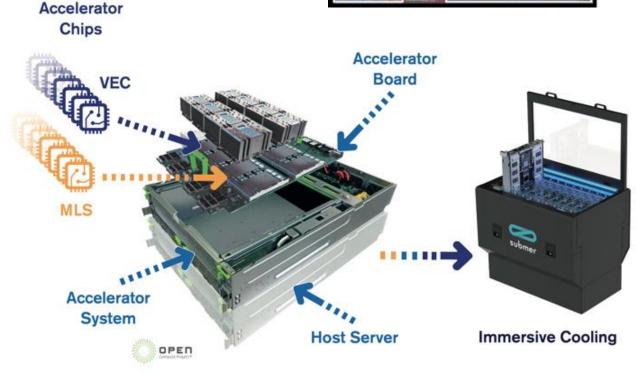

- EUPILOT

- Pilot RISC-V Accelerator Systems

- Many others not mentioned here...

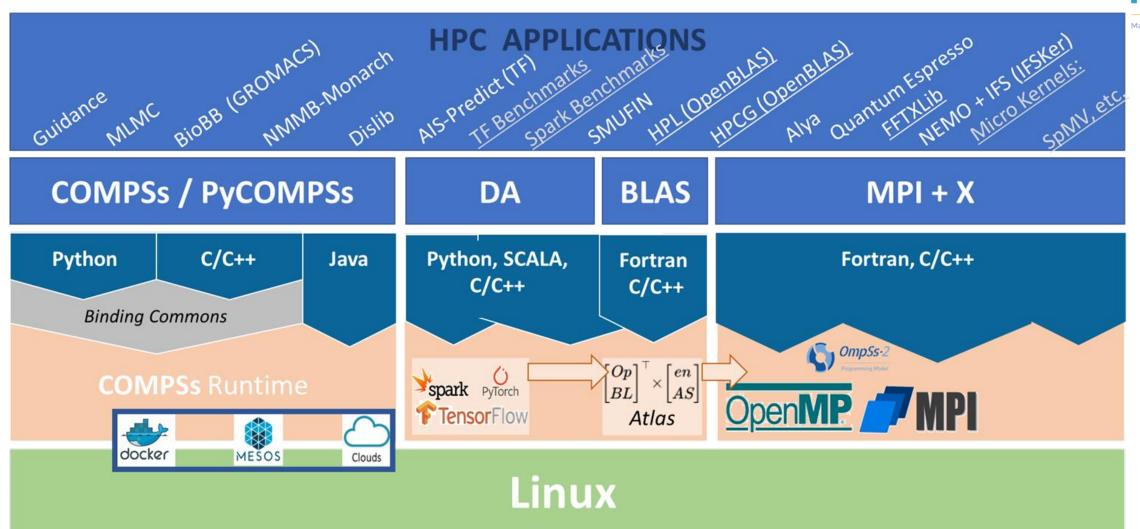

## **RISC-V Software Activities**

Exascale Platform

#### **RISC-V Software Activities**

# **RISC-V is HPC!**

## RISC-V Fan Favorite @ ISC'22 HPC Cluster Competition

- HPC Student Cluster Competition

- Bring your own cluster, < 3KW</li>

- Benchmarking

- HPCG, HPL, HPCC

- 3 Applications

- Compile and Run

- NWChem, ICON, Xcomact3d

- Secret application @ ISC: Fall3D

- Cluster from BSC (7) and Uni.

Bologna (6)

- 300 W cluster

- 1 GbE

- https://youtu.be/76VOM59bJkY

## **HPC RISC-V Companies**

#### Superscalar Out-of-Order Vector-capable Application cores:

- Akeana

- Alibaba

- Andes

- Axelera

- Esperanto (1000 vector core chip)

- InspireSemi (2560 core chip)

- Rivos

- Semidynamics

- SiFive

- TensTorrent (Ascalon core)

- Ventana (chiplets)

- + more (apologies for any missing names)

## **Next HPC RISC-V Project**

EuroHPC JU project announcement, Call published Dec 16<sup>th</sup>...

https://eurohpc-ju.europa.eu/framework-partnership-agreement-fpa-developing-large-scaleeuropean-initiative-high-performance\_en

Publication date: 15 December 2022

■ Opening date: 26 January 2023

Deadline date: 04 April 2023, 17:00 (CEST)

6 years, Multiple SGAs

#### Framework Partnership Agreement to:

- 1. RISC-V hardware: addressing the design, velocity ent, testing tape-out of different generations of energy efficient high-end processors and/or accelerators partition richiplet used approaches, for High Performance Computing (HPC), ...

- 2. integration in test-beds and reast e piles properational environments ...

- 3. RISC-V software: developed processors and/or accelerators....

- 4. Develop and/or adapt the ther necessary technologies for the integration of the RISC-V based components into industrial grade HPC solutions.

- 5. Identify the most critical polications and domains and work towards porting and optimising them for the new RISC-V based environment.

- 6. Explore and exploit existing manufacturing capabilities in Europe...

## Join us @ BSC

- Come help us build the Open HPC Ecosystem

- Engineers to Post Docs in:

- Applications

- Performance profiling & Tools

- System Software

- MPI & OpenMP

- LLVM Compiler

- Low-level software

- Computer Architecture

- RTL Design

- Design Verification

- FPGA Design & Implementation

- CAD tools

- HW & SW CI/CD

- Physical Design