# **Enabling Decentralised Machine Learning on RISC-**

Gianluca Mittone, Robert Birke, Iacopo Colonnelli, Marco Aldinucci Università degli Studi di Torino, Dipartimento di Informatica & CINI HPC Key Tecnologies and Tools lab

**EuroHPC**

### **Motivations**

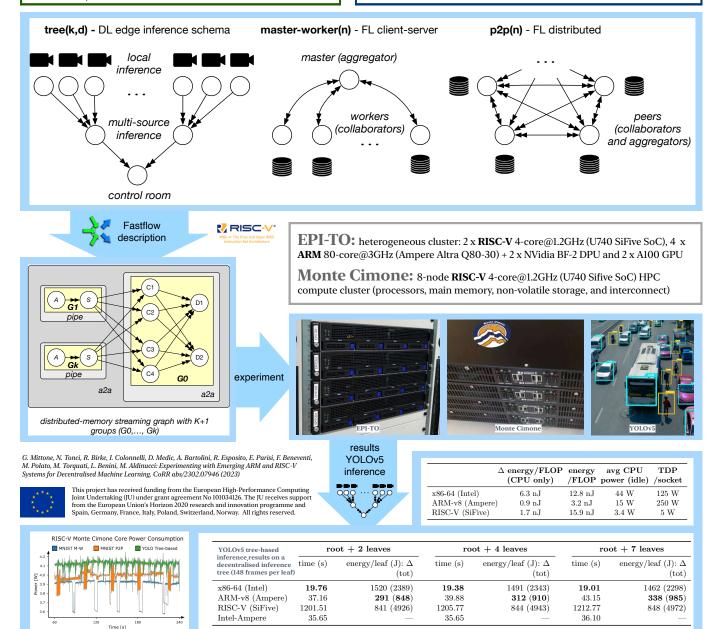

While tools for Decentralized ML are starting to flourish, many are not flexible and portable enough to experiment with novel systems (e.g., RISC-V), non-fully connected topologies, and asynchronous collaboration schemes. We present a methodology based on the FastFlow parallel programming library, capable of overcoming all these limitations and generating different working DML schemes on two emerging architectures (ARM-v8, RISC-V) and Intel.

#### Results

We propose a lightweight middleware for experimenting with FL at the edge. The proposed middleware comprises a run-time (FastFlow C++ header-only library) supporting the pattern-based generation of distributed streaming networks and a methodology to bring ML solutions often developed in Python to a C++ distributed system.

## Porting modern FL software on RISC-V

**PyTorch** (https://gitlab.di.unito.it/alpha/riscv/torch) Some of the PyTorch dependencies are still not compatible with the RISC-V ecosystem. Some of them are mandatory to complete the compilation process (breakpad, SLEEF). Others do not break the compilation process but affect some PyTorch core functionalities (<u>cpuinfo</u>). Others are compatible but not yet optimized.

**OpenFL** (https://github.com/alpha-unito/OpenFL-extended) OpenFL is an open-source FL framework developed by Intel. Despite officially not supporting RISC-V, we successfully made it work by recompiling ad hoc several Python packages (grpcio, scipy) and the OpenBLAS library.

#### FastFlow (https://github.com/fastflow)

FastFlow, being a vanilla C++20 header-only library, makes it possible to easily experiment with any distributed system having a working C++20 compiler, such as those based on Intel, ARM, or the emerging RISC-V architectures.