The EUPILOT project, part of Europe’s drive toward technological autonomy in High-Performance Computing (HPC), has reached a major milestone with the successful tape-out of its VEC and MLS chips, one targeted for HPC workloads and the other towards AI workloads. These achievements mark an important step toward demonstrating advanced accelerator platforms built on European research and collaboration.

Progress on VEC and MLC

Carlos Puchol (Barcelona Supercomputing Center – BSC), Principal Investigator of EUPILOT, emphasized that this milestone reflects the persistence and teamwork of the consortium:

“I’m pleased to share that EUPILOT VEC and MLS chips have recently taped-out on GF12 LP+ and TSMC7 respectively. This represents a major milestone for the project and reflects the hard work, collaboration, and persistence of everyone involved.

While tape-out is definitely not the finish line, it is an important step that brings us closer to demonstrating working accelerator platforms. Many challenges await during bring-up, validation, software, systems, and deployment; however, the collective effort that got us here gives us the stepping stones to continue forward.

Many contributed in design, verification, physical implementation, and more. Each piece of the puzzle was essential to reaching this point. The team will continue making progress in preparation of first silicon for both chips. In the meantime, let’s take a moment to recognize this achievement and the teamwork that made it possible. Onward to first silicon!”

Technical overviews

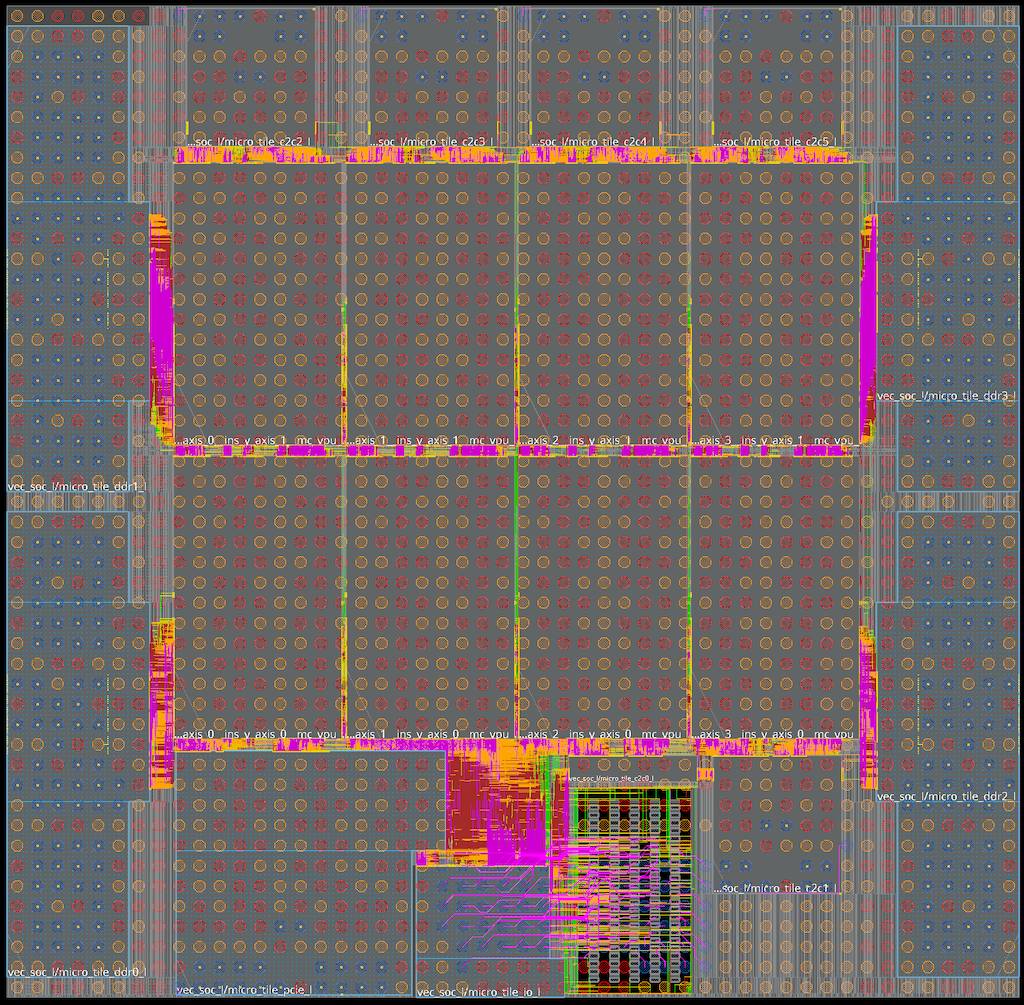

VEC

Jordi Fornt (BSC) provided an overview of the VEC chip, designed to support demanding vectorized and memory-intensive workloads:

- 8 cache-coherent 64-bit RISC-V cores, each with a 16-lane vector unit

- 4 LPDDR4 channels (68 GB/s total bandwidth)

- 5 chip-to-chip links (40 GB/s total bi-directional bandwidth)

- 1 PCIe channel (16 GB/s bi-directional bandwidth)

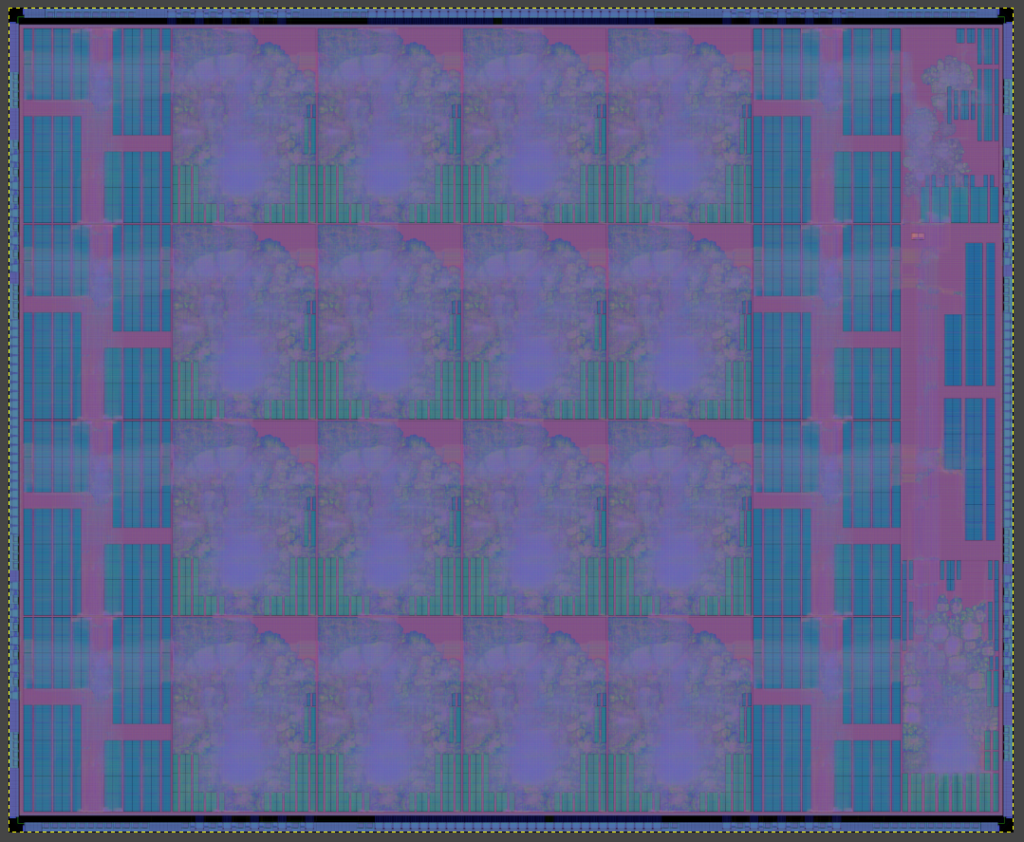

MLS

Tim Fischer (ETH Zurich) highlighted progress on Picobello:

“Picobello is the latest of the many-core architectures from ETH Zurich, based on the Snitch RV32 core. It contains 16 clusters with 9 cores each, an additional STX cluster, as well as more than 10 MB on-chip memory running at 1 GHz. It was made possible through the TSMC Academic Program supported by Europractice as part of the EUPILOT project. We expect the chip back in early 2026 and will publish the results once measurements have been completed.”

Next steps

The project now advances into the critical phase of silicon bring-up, validation, software enablement, system-level integration and datacentre deployment. These activities will be critical for turning the designs into fully functional accelerator platforms capable of supporting advanced HPC and AI workloads.

The challenges ahead are substantial, but the collaboration and persistence that enabled this achievement provide a strong foundation for what comes next. As EUPILOT moves into the final phase of the project, the consortium looks forward to sharing further progress and results with the community.

Bonus

Check out the chip gallery of the Integrated Systems Laboratory of ETH Zurich, brought to you by the Microelectronics Design Center.