Home /

Hardware

Hardware

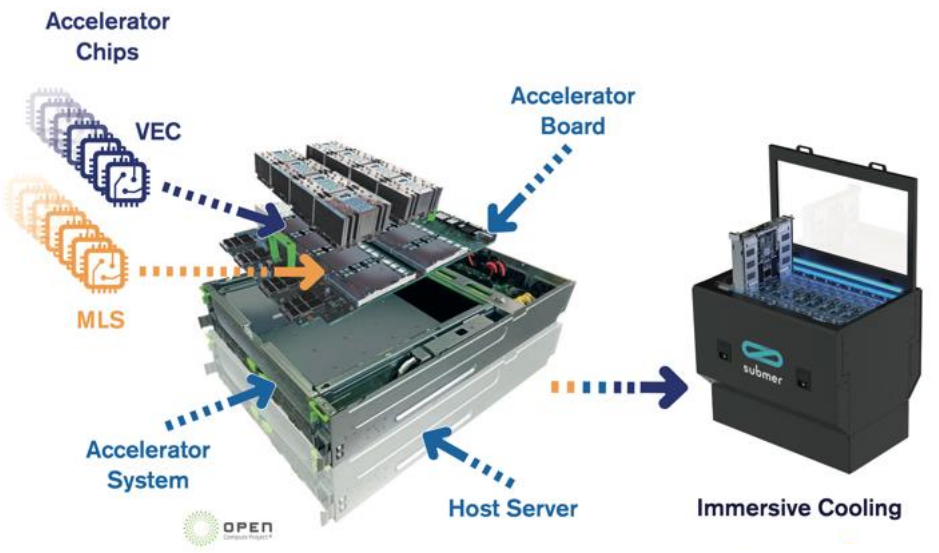

The EUPILOT project aims to build an end-to-end demonstrator of accelerators that could be used in a pre-exascale system. Making full use of European and open-source technologies and standards, the project will produce three chip tapeouts. The first tapeout will be a test chip to validate the use of the 12nm technology node, migrating down from previous 22 nm technology node tapeouts. The second and third tapeouts, developed concurrently, will contain a vector accelerator with up to 16 cores and a machine learning and stencil accelerator with up to eight cores, respectively.

The accelerator chips will be mounted along low-power double data rate (LPDDR) memory, forming the chip modules that will be installed into standard accelerator boards. We leverage the Open Compute Project Accelerator Module (OAM) standard to build the accelerator systems, which are paired with host servers. The combined host plus accelerators are deployed in liquid immersion tanks. These tanks efficiently support ultra-high power densities, the technology trend for the future of high-performance computers. Almost all of the hardware technology deployed in this system prototype is European.

What is EUPILOT's current status with hardware?

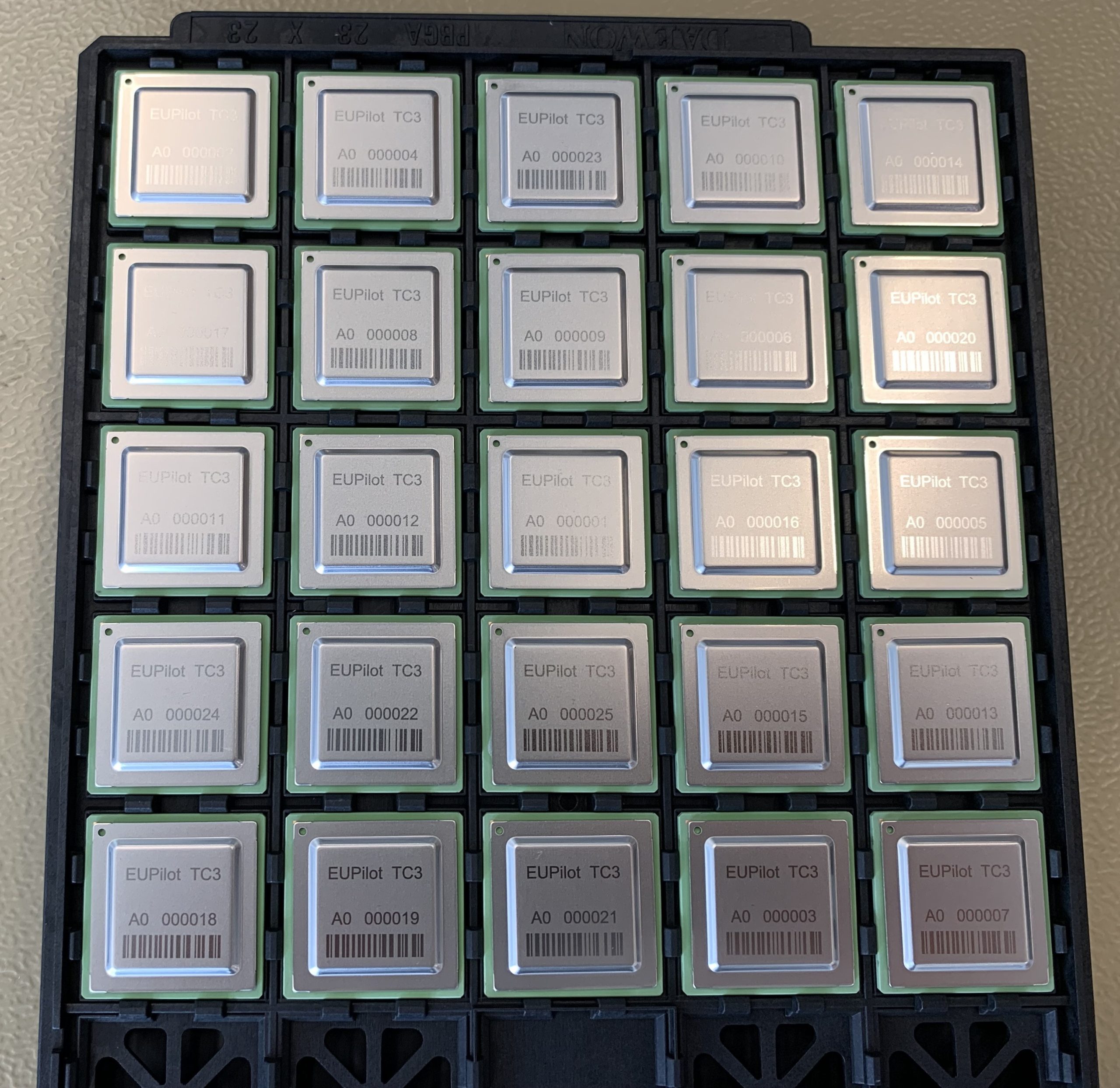

The tape-out has been completed and the first test-chip for the 12-nanometer technology node validation is received.

Currently, there is an ongoing evaluation on its architecture and interfaces. At the same time, preparations are being made for the tape-out of the VEC and MLS chips, targeted at HPC and AI applications, with continuous FPGA emulation enhancements to guarantee correctness and boost performance.