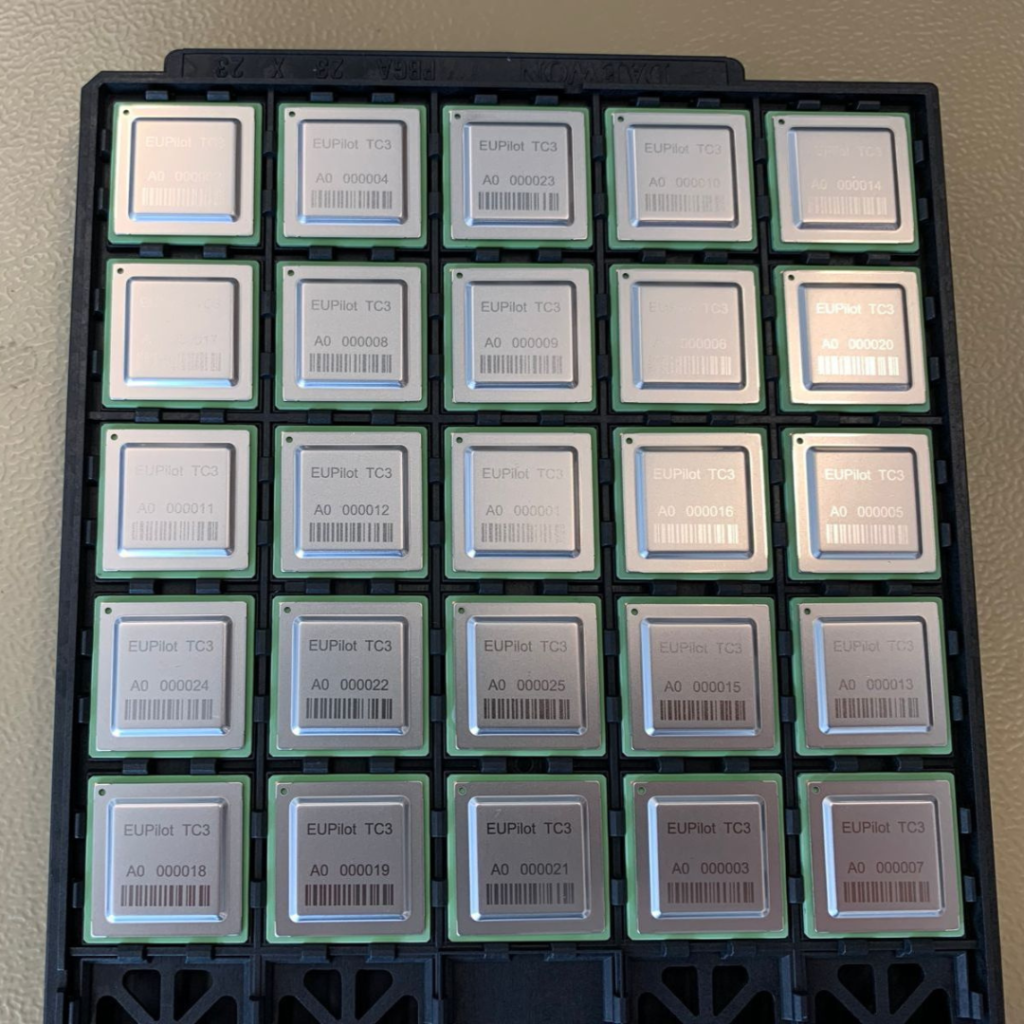

This month, the EUPILOT project marked a major milestone with the arrival of its first 12nm test chips. Designed by the EUPILOT team using GlobalFoundry’s 12nm FinFet technology, the chips include an LPDDR memory controller and interface with a deskew PLL for clocking and an FLL for power savings.

Image courtesy of EXAPSYS

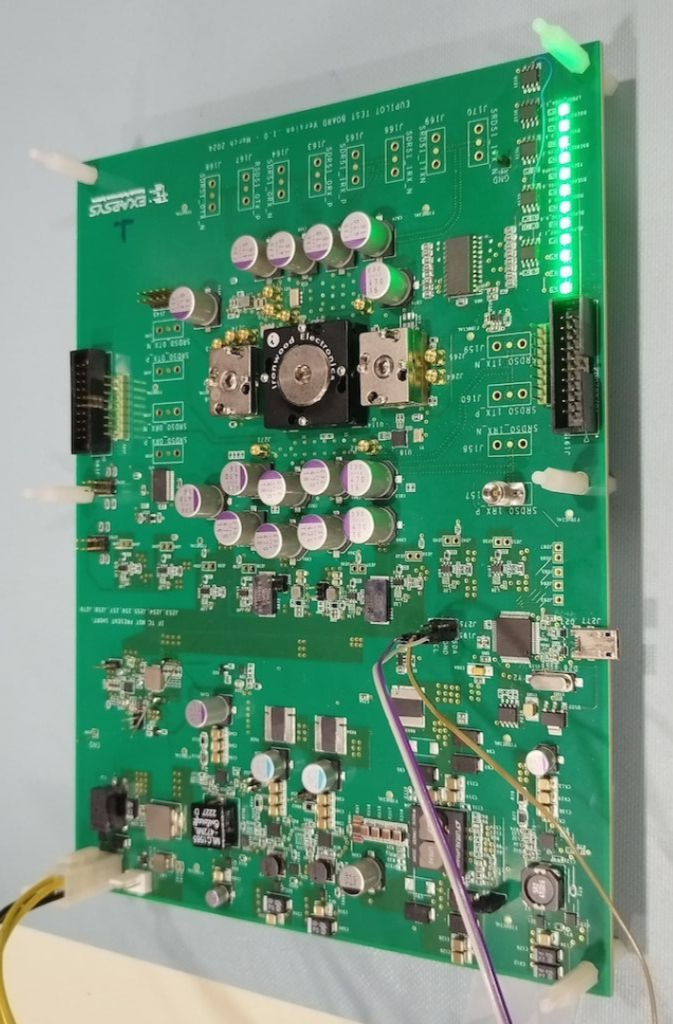

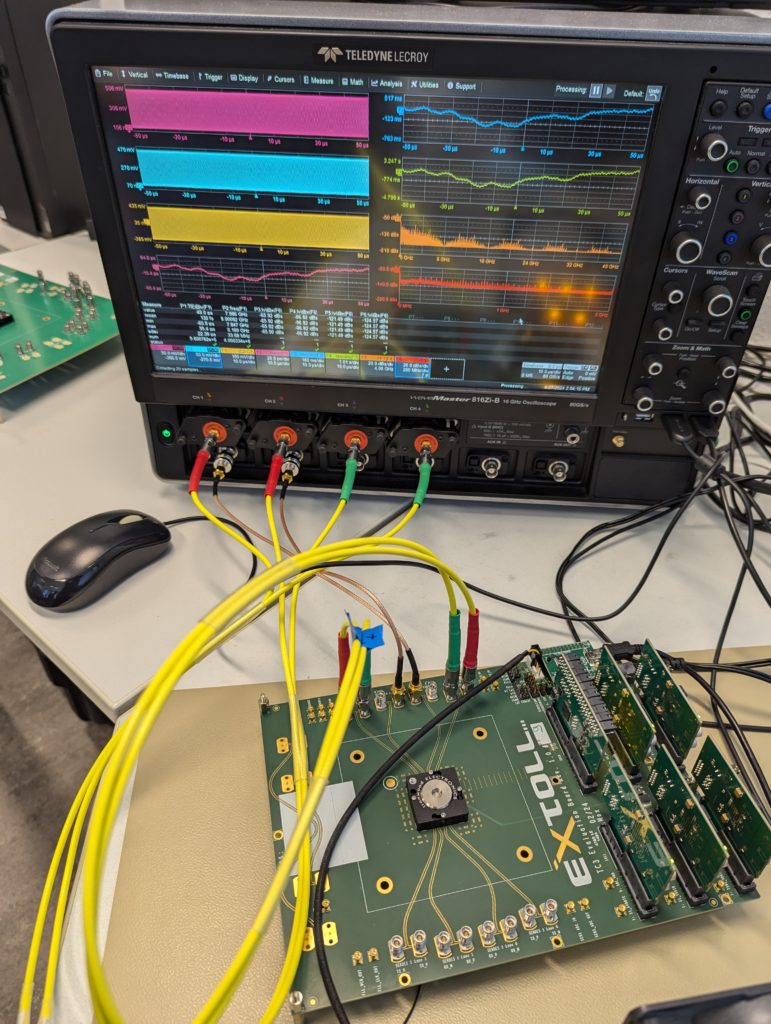

In the upcoming months, testing will continue in the various labs of the EUPILOT team consortium members. These chips are implemented for testing critical structures, from transistors to gates to analog circuits and IO receivers/transceivers, that will be of crucial importance for future tapeouts at this node. The images below show test boards that will be used for characterization in the coming weeks and months.

Image courtesy of EXAPSYS

Image courtesy of EXTOLL

Currently, in the initial days of testing, the chips are so far performing at the top frequency of 16 GHz. A number of test blocks are responding properly, and data is being transmitted across the SerDes/PHYs.

This step marks a significant milestone in the project’s development process. The EUPILOT team is eager to continue with testing and working towards the achievement of our targets.

Featured cover image courtesy of UNIPI. Images in the news piece courtesy of EXTOLL and EXAPSYS.